Intel's Compiler Update: Introduction of Xe-HPCVG and Ponte Vecchio VG Variants

Key Features of Xe-HPCVG and Ponte Vecchio VG

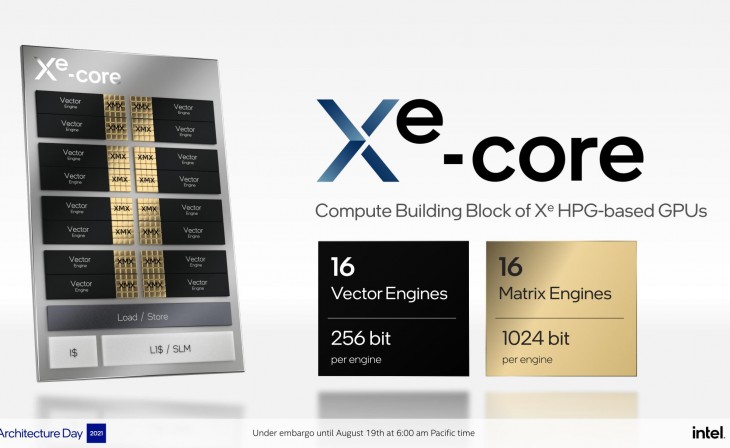

- Xe-HPCVG: Retains many features of the Xe-HPC architecture, such as 128KB shared local memory, FP64 computing, and BF16 support.

- Ponte Vecchio VG: Presents a variant of the original Ponte Vecchio but lacks DPAS (Dot Product Accumulate Systolic) instructions.

- Absence of DPAS: Both variants explicitly exclude DPAS instructions, which are crucial for AI and machine learning workloads.

The Implications of Missing AI Features

- AI Workload Impact: The lack of DPAS instructions, usually accelerated by XMX units, suggests these variants might not be optimized for AI workloads.

- Ponte Vecchio VG's Target Market: The absence of AI-accelerated features in Ponte Vecchio VG raises questions about its intended applications.

Also Check Comprehensive Review of Synology DiskStation DS220+ NAS

Speculation and Analysis

- Purpose of VG Variant: Intel might repurpose Ponte Vecchio chips with defective XMX units for a new GPU, or this could be an intentional feature limitation.

- Uncertainty of 'VG' Label: The meaning of 'VG' in this context is not clear, though it may align with terms like 'SDV' used in previous Intel products.

Performance and Comparison

- FP64 Performance: Despite lacking AI features, Ponte Vecchio VG still boasts a substantial 52 TFLOPs of FP64 performance.

- Comparison with Competitors: While impressive, its FP64 performance falls behind AMD's MI300X but surpasses Nvidia's H100.

Future of Intel's VG Variants

- Investment in Chip Technology: Ponte Vecchio represents Intel's significant investment in chip stacking and EMIB technologies.

- Anticipated Market Impact: The market's response to these VG variants, especially given the integral role of XMX instructions in compute tiles, remains to be seen.

Conclusion

Intel's update marks a notable shift in its graphics device offerings, particularly for those reliant on AI and machine learning capabilities. The Xe-HPCVG and Ponte Vecchio VG, with their exclusion of DPAS instructions, cater to a potentially different segment of the market. As Intel progresses, further details and the strategic intent behind these variants will likely emerge, shedding light on their role in the evolving landscape of graphics processing.